Submitted by Aegisx3 t3_zvwqyy in mildlyinteresting

Comments

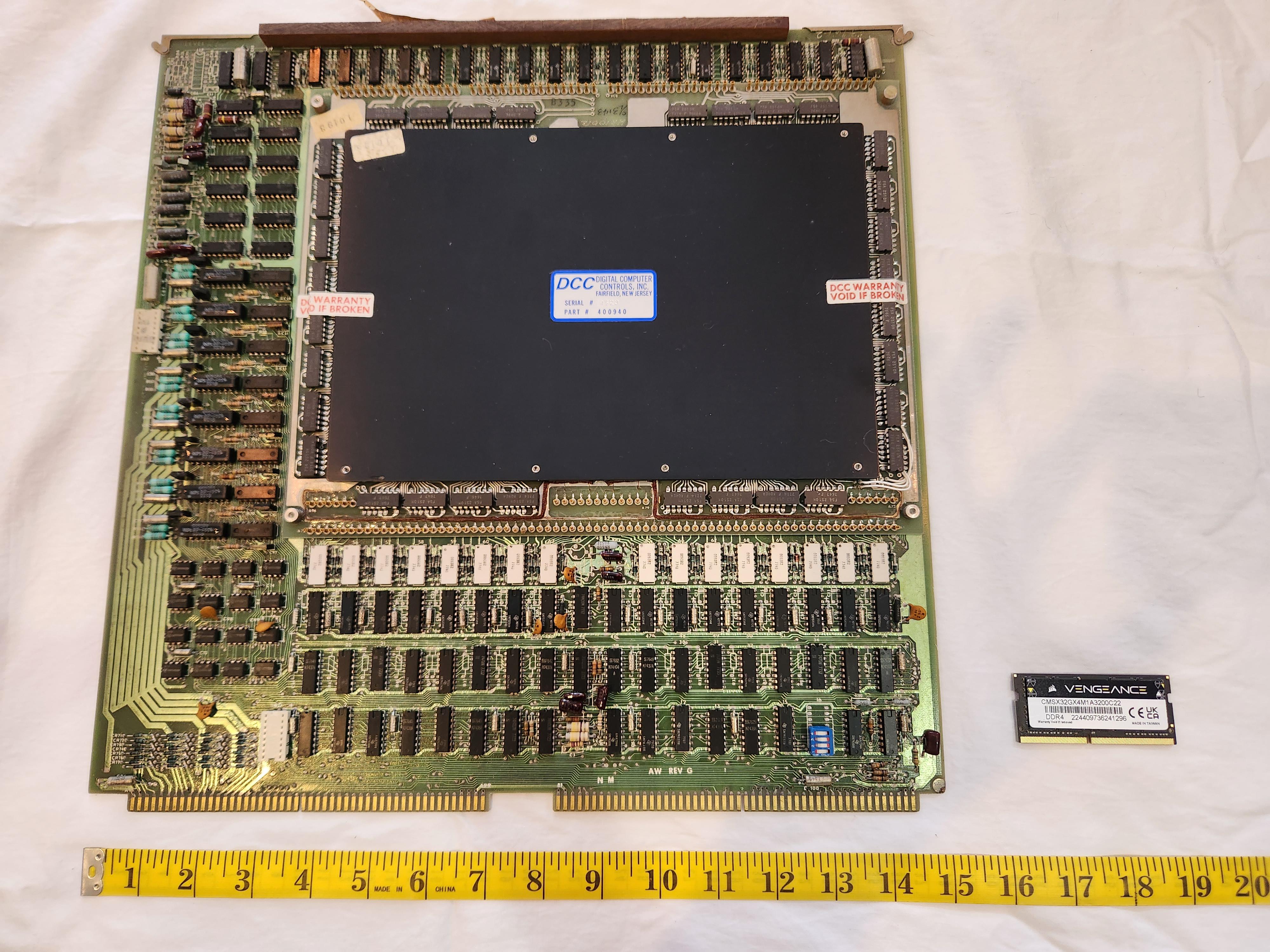

sopapillasopapilla t1_j1rla21 wrote

What was the price for 32kb of ram? $5,000?

f4f4f4f4f4f4f4f4 t1_j1rn317 wrote

To be faaiirr... The 1974 RAM board has control logic circuitry there, too. The modern RAM is controlled by a part in the system's CPU. You may compare the black shielded section to the modern RAM!

ARTICUNO_59 t1_j1rnc94 wrote

My brain blocked out the tape measure and thought that was a comically small stick of ram

cosmoboy t1_j1rofup wrote

https://jcmit.net/memoryprice.htm

If I did my math right, $10,666

Bubba-Fet t1_j1rpzme wrote

Take the black plastic cover off. You will see the ferrite core bits. An array of iron rings woven into memory.

sopapillasopapilla t1_j1rs631 wrote

$64,383.95 adjusted for inflation.

cosmoboy t1_j1rso36 wrote

That's what I paid for my 3080 that I play solitaire on.

Almost_a_circle359 t1_j1sjh5l wrote

What is a good speed comparison? That would probably depend on the bus speed of whatever it connected to but I am guessing that the modern RAM is generally just much faster anyway.

wkarraker t1_j1sptyf wrote

What system does this work in? Kinda looks like a RAMtek board from a Data General Eclipse S/280 expansion chassis I worked on back in the mid 80s. The black area reminds me of the 2K core memory.

Aegisx3 OP t1_j1svc6i wrote

As far as I can tell it's for a DCC-116. Unfortunately I don't have the front panel or chassis - just the backplane, CPU, cartridge disc controller, and a few other (potentially DG) boards I haven't identified yet. Probably won't ever happen but it'd be cool to bring the whole system together!

tokynambu t1_j1tq28j wrote

No, it isn’t. That is why cpus need a lot of pipelining and speculative execution and caching and the like.

Mid 1980s, the choice when buying asynchronous RAM was, if memory serves, 70ns or 35ns latency. That when a fast processor was less than 20MHz (a Sun 3/160 was a 68020 clocked at 16.67MHz). So one cycle was about 60ns, and processors did not need to wait for RAM.

Today synchronous memory has a first word latency of the order of 10ns; that isn’t exactly the same as asynchronous latency but approximately comparable. But the processor is running at, say, 3GHz. So now, instead of people able to read RAM in a clock cycle or at most two, you need 30 cycles to access RAM. Clock is ~100x faster, RAM latency is only ~3x better. The RAM is much faster in bulk transfer (perhaps 50x or more) which helps for some operations, but a single random read is not helped.

Hence cache, pipelines, speculative execution, caches, more caches.

Potatoswatter t1_j1u1gd1 wrote

That would void the warranty

Potatoswatter t1_j1u1qu0 wrote

Looks like decode logic. Core memory doesn’t need refresh like DRAM. It does need to be restored after reading, but it’s hard to say if this board implements that step or the CPU.

Potatoswatter t1_j1u2olv wrote

You just claimed that DDR5 SDRAM isn’t faster than magnetic core memory. Then you moved the starting point from core memory to mid-80’s DRAM, a completely different thing. Then gave the state of the art as 100ns when it’s more like 25ns if you stop to search. Then you still came up with 3x improvement in contradiction to the first sentence.

tokynambu t1_j1u53d8 wrote

That's a fair comment: I was comparing with the 80s, not the 70s.

However, I don't see how you get "Then gave the state of the art as 100ns" when I explicitly wrote "Today synchronous memory has a first word latency of the order of 10ns;"

JohnStern42 t1_j1rk8s7 wrote

Better not break that sticker or the warranty will be void!